#### **Product Features**

- 3.0 dB Slope

- Wide Bandwidth, DC-45 GHz

- Excellent Return Loss, 20 dB typ.

## **Typical Applications**

- Cellular Infrastructure

- 5G

- Wideband Communications

- Test Instrumentation

- Defense

### **General Description**

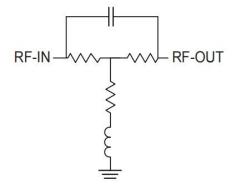

EQYT-3-453-D is an absorptive Gain Equalizer Die fabricated using highly repetitive GaAs IPD MMIC process incorporating resistors, capacitors and inductors having negative insertion loss slope. EQYT-3-453-D has a nominal attenuation slope of 3.0 dB.

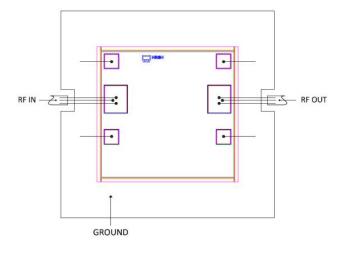

### Simplified Schematic and Pad description

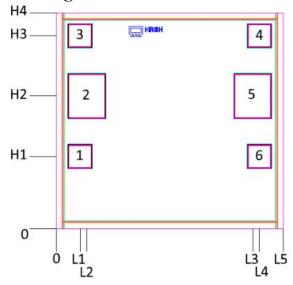

## **Bonding Pad Position**

| Pad Number | Function | Description   |    |     |     |     |     |     |        |     | T           |           |          |            |          |

|------------|----------|---------------|----|-----|-----|-----|-----|-----|--------|-----|-------------|-----------|----------|------------|----------|

| 2          | RF-IN    | RF-Input pad  |    | L2  | L3  | L4  | L5  | H1  | Dimens | H3  | μm, 1<br>H4 | Thickness | Die Size | Pad Size 2 | Pad Size |

| 5          | RF-OUT   | RF-Output pad |    |     | L3  | L4  | L5  | п   | ΠZ     | нз  | H4          | Thickness | Die Size | & 5        | 1,3,4,6  |

| 1,3,4,6    | GND      | Ground        | 78 | 101 | 649 | 672 | 750 | 239 | 439    | 639 | 715         | 100       | 750x715  | 117x142    | 72x72    |

EQYT-3-453-D

**Gain Equalizer Die**

# EQYT-3-453-D

Gain Equalizer Die 50Ω 3dB DC to 45 GHz

## Electrical Specifications<sup>1</sup> at 25°C, 50Ω, unless otherwise noted.

| Parameter       | Condition<br>(GHz)                                    | Min. | Тур.                                   | Max. | Units |  |

|-----------------|-------------------------------------------------------|------|----------------------------------------|------|-------|--|

| Frequency Range |                                                       | DC   |                                        | 45   | GHz   |  |

| Insertion Loss  | 0.01<br>10<br>20<br>30<br>40<br>45                    |      | 4.6<br>4.3<br>3.6<br>2.4<br>1.0<br>1.1 |      | dB    |  |

| VSWR            | 0.01 - 10<br>10 - 20<br>20 - 30<br>30 - 40<br>40 - 45 |      | 1.14<br>1.15<br>1.22<br>1.23<br>1.20   |      | :1    |  |

1. Electrical specifications are typical measured using MPI Titan Series 200um pitch GSG probe.

## Absolute Maximum Ratings<sup>2</sup>

| Operating Case<br>Temperature | -55°C to 105°C |

|-------------------------------|----------------|

| RF Input Power <sup>3</sup>   | 30dBm          |

2. Permanent damage may occur if any of these limits are exceeded.

3. Derates linearly to 26 dBm at  $105^{\circ}$  C

## Assembly and Handling Procedure

#### 1. Storage

Dice should be stored in a dry nitrogen purged desiccators or equivalent.

2. ESD

MMIC GaAs Gain equalizer dice are susceptible to electrostatic and mechanical damage. Die are supplied in antistatic protected material, which should be opened in clean room conditions at an appropriately grounded anti-static worksta tion. Devices need careful handling using correctly designed collets, vacuum pickup tips or sharp antistatic tweezers to deter ESD damage to dice.

#### 3. Die Attach

The die mounting surface must be clean and flat. Using conductive silver filled epoxy, recommended epoxies are DieMat DM6030HK-PT/H579 or Ablestik 84-1LMISR4. Apply sufficient epoxy to meet required epoxy bond line thickness, epoxy fillet height and epoxy coverage around total die periphery. Parts shall be cured in a nitrogen filled atmosphere per manufacturer's cure condition. It is recommended to use antistatic die pick up tools only.

4. Wire Bonding

Bond pad openings in the surface passivation above the bond pads are provided to allow wire bonding to the dice gold bond pads. Thermosonic bonding is used with minimized ultrasonic content. Bond force, time, ultrasonic power and temperature are all critical parameters. Suggested wire is pure gold, 1 mil diameter. Bonds must be made from the bond pads on the die to the package or substrate. All bond wires should be kept as short as low as reasonable to minimize performance degradation due to undesirable series inductance.

## **Assembly Diagram**